動作原理

TANACOM-1 が命令を実行する仕組み

TANACOM-1 の中で、命令はどうやって実行されて行くのでしょう。それをご説明いたします。

一般的にコンピューターが、命令を実行すると言うのは、

- フェッチサイクル ・・・メインメモリから命令を取り出す。

- デコード・・・命令の解読(解釈)

- エグゼキュートサイクル ・・・実行

でありまして、停止の指示があるまで、これを繰り返します。

TANACOM-1 でも、全く同じです。

具体的には、この動作を制御装置の Phase Control が担当します(回路図は、こちらです)。

この回路が、TANACOM-1 の中で一番大切な回路です。

まず、回路図をご覧頂きますと解りますが、水晶発振器を使ったクロック回路にて、10 MHzのパルスが作られます。1周期は、100 nSになります。

これを3進カウンタに通し、300 nSのパルスに変換します。このパルスが、TANACOM-1 を順序よく、決められた通りに動かすための、「号令」の基本となります。

その先に、D型フリップフロップ(以下、D-FF と表現)を連ねて、循環させた回路があります。一番先頭のD-FF には、「M1」と名前がついています。

このD-FF 達が、300 nSの号令に従い、まるでドミノ倒しのように、順繰り、順繰り、300 nSごとに動いていきます。

一番、最後のD-FF の信号は、一番先頭のD-FF に接続されていますので、「停止」の指示があるまで、

永遠に循環します。

このD-FF について、先頭から順番に、

- フェッチサイクル

- デコード

- エグゼキュートサイクル

と、役割を割り当てやり、ぐるぐると循環させれば、あっという間にコンピューターと称されるマシンがそこに誕生します。どうです、とても簡単でしょ!

実際は、より便利で、もっと複雑な動きが出来るように、さらなる役割を持たせたD-FF を追加してあります。

また、「デコード」という、命令を解釈する行程は、短時間で出来ますので、フェッチサイクルの行程終り付近で「デコード」作業をさせ、独立したD-FF は使いませんでした。

それでは、より具体的にご説明いたします。

TANACOM-1 の命令は、次の3つの系統があります。

< メモリ参照命令系 >

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0 | OP Code | R1/ R0 |

Ix | Id | M/ im |

Address or immediate | |||||||||

< ブランチ命令系 >

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 1 | OP Code | CNT | Ix | Id | C/ Z |

Address | |||||||||

< コントロール命令系 >

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 1 | 1 | 1 | 1 | OP Code | Operand | ||||||||||

これらを組み合わせて、目的の動作をさせるために、メモリ上に書き込まれたプログラムの1命令、1命令について、制御装置は、次の様に実行していきます。

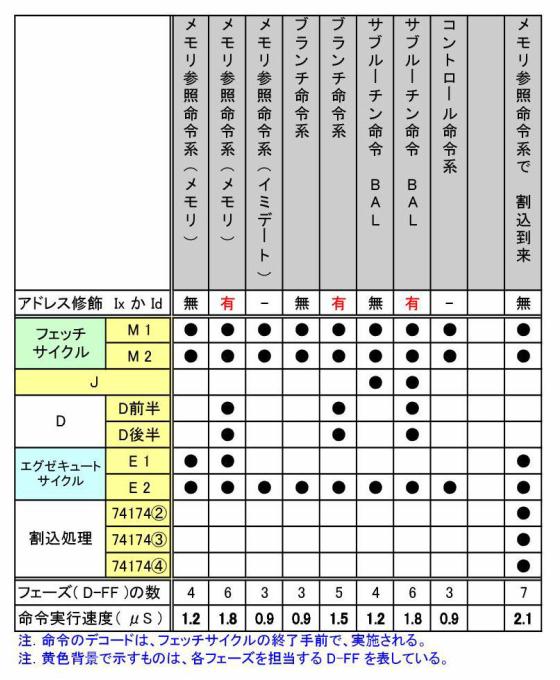

赤文字で示した記号は、役割を割り当てた1個1個のD-FF の名称を表しています。

但し、「D」については、直列につないだ、2個のD-FF で構成されています。

TANACOM-1 のメインメモリに採用したSRAMは、アクセスタイムが、450 nSでした。

そこで、メモリアクセスを必要とするフェーズには、必ずD-FF が2個関わる(2個で600 nSを作り、450 nSをしっかりカバーする)様に設計しました。

TANACOM-1 の先の3系統の命令達は、命令の性格により、また条件により、使うD-FF 違ってきます。

それを表にまとめてみました。

フェッチサイクルである M1+M2 だけは、皆同じです。

TANACOM-1 は、この様に、最速で 0.9μS、遅くても1.8μSで、命令が処理されている事が解ります(割込の場合を除く)。

また、目的の動作を「実行」するエグゼキュートサイクルに於いて、メモリアクセスに関わらない、ブランチ命令系、コントロール命令系、イミデートを使うメモリ参照命令系は、1個のD-FF( E2 )で済むようにして、少しでも命令実行速度を稼ぐように、工夫しました。

アクセスタイムの早い SRAMを使える様になれば、この制御装置の Phase Control は、大きく変わるでしょう。

実は、この回路をどう設計するかが、コンピューター設計者の腕の見せ所です。

皆様も、ぜひ、やってみませんか?

クロック回路のタイミング詳細

具体的にクロック回路の動作を解説いたします。

前項で説明しました Phase Control に於いて、水晶発振器にて作られた 10 MHzのパルスは上図の、①から入って来ます。1周期は、100 nSになります。

その 100 nSのパルスが、2個のJKフィリップフロップ( 以下 JK-FF )で構成される3進カウンタを通ると、その出力②、③は、

のようになります。

②、③は、3進カウンタの出力ですから、当然、その周期は 300 nS になります。

さあ、ここで制御回路は、この②のパルスの立ち上がり( ポジティブ・エッジ )を利用して、先のフェーズ用D-FFを順序よく動かしていきます。

そして、③を正式なCLOCK信号として、各レジスタやカウンタに、送り出します。

各レジスタ等は、③CLOCKパルスの立ち下がり( ネガティブ・エッジ )で、動作確定するように配線されています。

上図の最後は、各フェーズのD-FFが循環していくタイミング例を概念的に表現してみました。

この絵のごとく、各フェーズとフェーズの切り替わり点では、微妙に両者の信号が重なり合うシーンが見られます。

しかし、全ての動作は、③CLOCKパルスのネガティブ・エッジでしか起こりませんので、その時点で、全ての信号は安定した状態にあり、重なったり混線する事は、絶対に起こらないのです。